# Abridged version

# KAWASAKI STEEL TECHNICAL REPORT

No.30 (August 1994) Special Issue on LSI

Improving Gate Oxide Integrity in p+pMOS Devices by Using Large Grain Polysilicon Gate

Munetaka Koda, Junichi Kawaguchi, Yoshikatsu Shida

# Synopsis:

The effect of polysilicon grain size on gate oxide integrity in BF2 implanted polysilicon gate pMOS devices was investigated by measuring the electrical characteristics of a MOS capacitor. Gate oxide integrity deteriorated when conventional polysilicon with a small (0.05µm) grain size was used. The use of large (1.0µm) grain polysilicon was effective in solving this problem of gate oxide quality. Additionally, the use of large grain polysilicon greatly reduced boron diffusion through the gate oxide into the channel region and decreases in gate oxide capacitance.

(c)JFE Steel Corporation, 2003

The body can be viewed from the next page.

# Improving Gate Oxide Integrity in p\*pMOS Devices by Using Large Grain Polysilicon Gate\*

Munetaka Koda Senior Researcher, LSI Research Center, High-Technology Res. Labs., Technical Res. Div.

Junichi Kawaguchi LSI Research Center, High-Technology Res. Labs., Technical Res. Div.

Yoshikatsu Shida LSI Research Center, High-Technology Res Labs., Technical Res. Div.

### Synopsis:

The effect of polysilicon grain size on gate oxide integrity in  $BF_2$  implanted polysilicon gate pMOS devices was investigated by measuring the electrical characteristics of a MOS capacitor. Gate oxide integrity deteriorated when conventional polysilicon with a small  $(0.05 \, \mu m)$  grain size was used. The use of large  $(1.0 \, \mu m)$  grain polysilicon was effective in solving this problem of gate oxide quality. Additionally, the use of large grain polysilicon greatly reduced boron diffusion through the gate oxide into the channel region and decreases in gate oxide capacitance.

#### 1 Introduction

As CMOS technology is scaled down to dimensions of below  $0.5 \,\mu\text{m}$ , it is necessary to use n<sup>+</sup> polysilicon gates on nMOSFET and p<sup>+</sup> polysilicon gates on pMOSFET so that both devices act as surface channel transistors with proper short-channel characteristics. 1,2) The simplest process for fabricating such dual gate CMOS devices is to dope the polysilicon gate after they are patterned with the same implants as the n+ and p+ source-drain implants.3) This not only minimizes the number of masks but also avoids the problem of different n<sup>+</sup> and p<sup>+</sup> polysilicon etch rates when doping is done before patterning. However, many problems with p+pMOSFET were reported. When BF2 is used for gate-S/D co-ion implantation, the fluorine enhances boron penetration through the gate oxide into the channel region.<sup>4)</sup> This boron penetration results in a positive shift in the p-channel threshold voltage. Fluorine reduced the dielectric constant of oxide and decreased gate oxide capacitance. 5,6) Furthermore, we have found that gate oxide in a low BF2-implanted polysilicon gate capacitor showed low-voltage breakdown.71 In this paper, the problems with p<sup>+</sup>pMOSFET are shown to be related to the grain size and structure of polysilicon. Thus, problems such as gate oxide deterioration, boron penetration, and low oxide capacitance can be solved by using large grain polysilicon.

### 2 Experimental

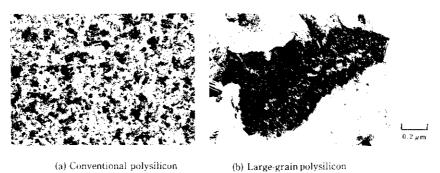

The effect of the grain size and structure of polysilicon on gate oxide integrity, boron penetration, and gate oxide capacitance was investigated. The MOS capacitors used in the study were fabricated as follows: A scarified oxide was stripped and RCA-cleaning was performed immediately prior to growth of the gate oxide on a (100) n-type silicon substrate. For the gate oxide, 8 nm silicon dioxide and nitrided oxides were used. Nitridation of the silicon dioxide was performed in N<sub>2</sub>O. Immediately after oxide growth, a 150 nm undoped silicon film was deposited, and the grain size and structure of this film were controlled by changing the film-formation conditions as shown in Table 1. An amorphous silicon film was deposited at 480°C by using Si<sub>2</sub>H<sub>6</sub> gas and crystallized at 650°C for 5 h to form large grain polysilicon. Planar TEM photographs of conventional and large grain polysilicon samples are shown in **Photo 1**. The

Table 1 Conditions for polysilicon film formation

| :                        | CVD                            |             | A                     |

|--------------------------|--------------------------------|-------------|-----------------------|

|                          | Source gas                     | Temperature | Annealing             |

| Conventional polysilicon | SiH₄                           | 620°C       |                       |

| Large-grain polysilicon  | Si <sub>2</sub> H <sub>6</sub> | 480°C       | 650°C<br>for 5 h in N |

<sup>\*</sup> Originally published in Kawasaki Steel Giho, 26(1994)2, 81-85

Photo 1 TEM plan-views of the polysilicon film

average grain sizes of conventional polysilicon (small grain) and large grain polysilicon are on the order of  $0.05~\mu m$  and  $1.0~\mu m$ , respectively. The undoped polysilicon was then oxidized (4 nm in thickness) and implanted with BF<sub>2</sub>. After LTO and BPSG had been deposited, the samples were annealed at 900°C for 30 min in N<sub>2</sub> to activate the dopant.

A time-zero dielectric breakdown (TZDB) test was performed on 108 capacitors with an active area of 4 mm<sup>2</sup>. The gate oxide breakdown voltage is defined as the voltage required for a current density of 32 mA/cm<sup>2</sup> to flow through the capacitor. A constant current time-dependent dielectric breakdown (TDDB) test was also performed on 108 capacitors with an area of 1 mm<sup>2</sup>. Capacitance measurement was performed on a MOS capacitor with an active area of 0.25 mm<sup>2</sup> to study boron penetration and decrease of gate oxide capacitance.

# 3 Results and Discussion

# 3.1 Gate Oxide Quality

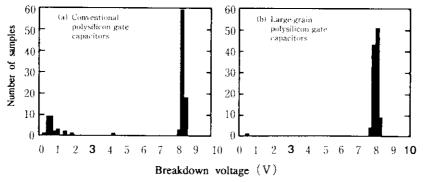

Figure 1 shows breakdown histograms for conventional and large grain polysilicon gate capacitors with the 8 nm nitrided oxide. This figure indicates that the gate oxide quality of the capacitor with conventional polysilicon was inferior to that with large grain polysilicon. In 26% of capacitors with a conventional polysili-

con gate, the gate oxide shows low-voltage (below 2 V) breakdown. The oxide defect density was calculated to be as high as 7.5 cm<sup>-2</sup>. This inferior quality was improved by using large grain polysilicon. The number of gate oxide breakdowns at low voltage decreased, and the gate oxide in almost all capacitors showed breakdown at high-voltage. In this case, the defect density was as low as 0.3 cm<sup>-2</sup>.

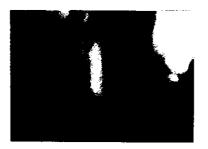

It is believed that the bad gate oxide quality in conventional polysilicon is brought about not by any degradation of oxide quality, but by the generation of weak spots in the gate oxide. Photo 2 shows dark field TEM micrographs of the small grain and large grain polysilicons. The direction of the electron beam was parallel to the interface between the polysilicon and gate oxide, which coincides with the [101] direction of the silicon substrate. The interface between the polysilicon and gate oxide is as smooth as that between the gate oxide and silicon substrate in large grain polysilicon gate MOS capacitor. On the contrary, gate oxide thinning occurred in conventional polysilicon gate MOS capacitors. Low voltage breakdown in conventional polysilicon gate MOS capacitors could occur at the points. The mechanism of this phenomena can be explained as follows: When the polysilicon films were oxidized and annealed, a compressive stress was generated in the polysilicon film by expansion of polysilicon grain boundary. Oxidizing and annealing process resulted in a Raman peak

Fig. 1 Histograms for the time-zero dielectric breakdown voltage of gate oxide capacitors with 8 nm nitrided oxide

L\_\_\_\_\_\_30 mm

(a) Conventional polysilicon

(b) Large-grain polysilicon

Photo 2 Dark-field TEM micrographs

(a)As deposited polysilicon

(b)Phosphorus-doped polysilicon

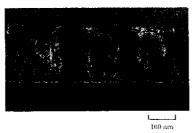

Photo 3 Cross-sectional TEM micrographs of the polysilicon films

shift to a higher wave number by  $1.0 \text{ cm}^{-1}$ , which corresponds to a stress of  $2.5 \times 10^9 \text{ dyn/cm}^2(2.5 \text{ MPa})$ . Wedge-shaped grains were found clinging to the gate oxide in the polysilicon. The grains were pushed into the gate oxide by the compressive stress during oxidization and annealing.

This was a unique phenomenon observed in BF<sub>2</sub> implanted polysilicon gate pMOS devices. Boron has no effect on the enhancement of the grain growth during heat treatment, which is contrary to the results with phosphorus and arsenic doped polysilicon.<sup>8)</sup> Wedgeshaped grains, which existed in as-deposited polysilicon, did not disappear during heat treatment because of insufficient grain growth.

On the contrary, grain-growth occur easily and wedge-shaped grains disappear in phosphorus and arsenic doped polysilicon. **Photo 3** shows TEM micrographs of the phosphorus doped polysilicon. Large grain polysilicon had no wedge-shaped grains under a deposited condition similar to that for phosphorus doped polysilicon, and good gate oxide quality was obtained.

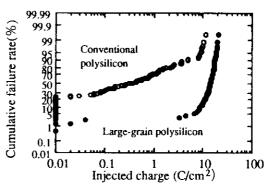

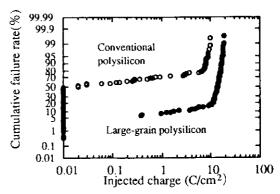

Figures 2 and 3 show the cumulative failure vs. charges to breakdown  $(Q_{\rm bd})$  in capacitors with nitrided oxide and silicon dioxide, respectively. In Fig. 2, the gate oxide in 30% of the capacitors with a conventional polysilicon gate shows breakdown immediately after a voltage was applied to the capacitor. On the other hand, the large grain polysilicon gate capacitors showed superior gate oxide quality in the random failure region, which explains the results presented in Fig. 2. A similar result was also obtained for the 8 nm silicon dioxide

Fig. 2 Cumulative failure vs injected charge to breakdown for conventional and large-grain polysilicon gate capacitors with 8 nm nitrided oxide

Fig. 3 Cumulative failure vs injected charge to breakdown for conventional and large-grain polysilicon gate capacitors with 8 nm wet oxide

capacitors as shown in Fig. 3.  $Q_{\rm bd}$  at 50% failure with the large grain polysilicon gate capacitor is twice as large as that in the conventional polysilicon type. The use of the large grain polysilicon gate lowered the gate oxide defect density and improved the gate oxide reliability.

### 3.2 Boron Penetration through Gate Oxide

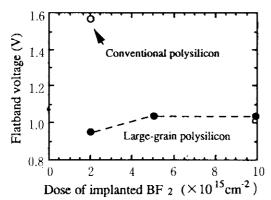

Figure 4 shows the relationship BF2 dosage and flatband voltage for the capacitors with 8 nm wet oxide. BF<sub>2</sub> ions were implanted at the dosage of  $2 \times 10^{15} / \text{cm}^2$ and annealed at 900°C for 30 min. The flatband voltage of the capacitor without boron penetration was measured as 0.95 V from the work function difference between the silicon substrate and p<sup>+</sup> polysilicon. The flatband voltage of the large grain polysilicon gate capacitor was 0.95 V at a BF<sub>2</sub> dosage of  $2 \times 10^{15}$ /cm<sup>2</sup>, which means boron had not penetrated. However, the flatband voltage of the conventional polysilicon gate MOS capacitor was 1.55 V at the same dosage of BF<sub>2</sub>, which means boron had penetrated. The large grain polysilicon gate suppressed boron penetration. The flatband voltage of the large grain polysilicon gate capacitor was 1.05 V and 1.02 V at dosages of  $5 \times 10^{15}$  and  $1 \times 10^{16}$ /cm<sup>2</sup>, respectively. The flatband voltage increase from 0.95 V could be not due to boron penetration but due to a negative charge generated in the gate oxide.

Fig. 4 Flatband voltage as a function of BF<sub>2</sub> dosage for conventional and large-grain polysilicon gate capacitors with 8 nm wet oxide

# 3.3 Gate Oxide Capacitance and Inversion Capacitance Decrease

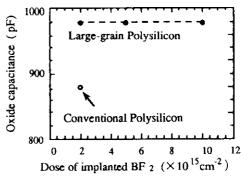

Figure 5 shows the relationship between gate oxide capacitance ( $C_{\rm ox}$ ) at a gate voltage of 3.3 V and BF<sub>2</sub> dosage. A heavy phosphorus doped polysilicon gate MOS capacitor, whose capacitance was 1 nF, was used as a reference. The capacitance of the large grain polysilicon gate was 980 pF, which was 2% smaller than the reference capacitance. In contrast, the capacitance of a conventional polysilicon gate was 12% smaller than the reference capacitance. The large capacitance decrease in

Fig. 5 The effect of implant dosage of BF<sub>2</sub> on oxide capacitance for conventional and large-grain polysilicon with 8 nm wet oxide

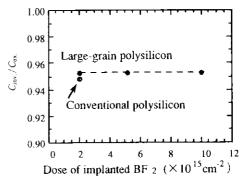

Fig. 6 C<sub>inv</sub>/C<sub>ox</sub> as a function of BF<sub>2</sub> dosage for conventional and large-grain polysilcon gate capacitors with 8 nm wet oxide

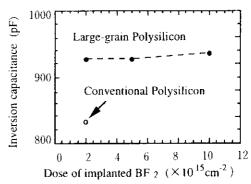

Fig. 7 The effect of dosage of BF<sub>2</sub> on inversion capacitance for conventional and large-grain polysilicon with 8 nm wet oxide

conventional polysilicon gate MOS capacitors occurs due to a dielectric constant decrease or additional gate oxide growth at a high level of fluorine. Figures 6 and 7 shows the BF<sub>2</sub> dosage dependence of  $C_{\rm inv}/C_{\rm ox}$ , and that of  $C_{\rm inv}$ , respectively.  $C_{\rm inv}$  means the capacitance of an MOS capacitor at the inversion condition from quasi-

static CV measurement, and  $C_{\rm inv}/C_{\rm ox}$  is a parameter which is related to the carrier concentration in the polysilicon.  $C_{\rm inv}/C_{\rm ox}$  shows little difference in the two types of polysilicons. However, the  $C_{\rm inv}$  of large grain polysilicon gate MOS capacitors differs from that of conventional polysilicon gate MOS capacitors. Large grain polysilicon gate suppress the decrease in gate oxide capacitance and inversion capacitance.

### 4 Conclusions

The effect of polysilicon grain size and morphology on gate oxide integrity, boron penetration, and gate oxide capacitance in p<sup>+</sup>pMOS devices was investigated, with the following results:

- (1) Conventional polysilicon (0.05  $\mu$ m) degraded gate oxide integrity.

- (2) The use of large grain  $(1.0 \,\mu\text{m})$  polysilicon gates solved the problem of poor gate oxide quality.

- (3) The low gate oxide quality of conventional polysilicon gate MOS capacitors is possibly attributable to gate oxide thinning, which can be suppressed by the use of a large grain polysilicon gate.

- (4) Large grain polysilicon prevented boron diffusion through the gate oxide.

- (5) Large grain polysilicon gates suppressed gate oxide capacitance decreases.

#### References

- B. Davari, W. H. Chang, M. R. Wordeman, C. S. Oh, Y. Taur, K. E. Petrillo, D. Moy, J. J. Buchignano, H. Y. Ng, M. G. Rosenfield, F. J. Hohn, and M. D. Rodrigues: "A High Performance 0.25 μm CMOS Technology," IEDM Technical Digest, San Francisco (USA), (1988), 56

- R. A. Champman, C. C. Wei, D. A. Bell, S. Aur, G. A. Brown, and R. A. Haken: "0.5 Micron CMOS for High Performance at 3.3 V," IEDM Technical Digest, San Francisco (USA), December (1988), 52

- 3) J. Y. C. Sun, Y. Taur, R. H. Dennard, and S. T. Klepner: *IEEE Trans. Electron Device*, ED-34 (1987), 19

- H. H. Tseng, P. J. Tobin, F. K. Baker, J. R. Pfiester, K. Evans, and P. Fejes: "The Effect of Silicon Gate Micro Structure and Gate Oxide Process on Threshold Voltage Instability in BF<sub>2</sub> Implanted P-channel MOSFETs," 1990 Symposium on VLSI Technology, Honolulu (USA), (1990), 111

- F. K. Baker, J. R. Pfiester, T. C Mele, H. H. Tseng, P. J. Tobin, J. D. Hayden, C. D. Gunderson, and L. C. Parrillo: "The Influence of Fluorine on Threshold Instability in p<sup>+</sup> Polysilicon Gated P-channel MOSFETs," IEDM Technical Digest, Washington, D.C. (USA), (1989), 443

- P. J. Wright and K. C. Saraswat: *IEEE Trans. Electron. Devices*, 36(1989), 879

- M. Koda, Y. Shida, J. Kawaguchi, and Y. Kaneko:, "Improving Gate Oxide Integrity in p<sup>†</sup>pMOSFET by Using Large Grain Size Polysilicon Gate," IEDM Technical Digest, Washington, D.C. (USA), (1993), 471

- L. Mei, M. Rivier, Y. Kwark, and R. W. Dutton: J. Electrochemical Society, 129 (1982), 1791